The performance of a product operating at high frequencies depends largely on the electrical characteristics of the Printed Circuit Board (PCB) used for mounting and connecting its circuit components. The magnitude of the impact of the PCB design increases exponentially with increase of the operational frequency. Therefore, designers need to include electrical models of PCB structures when simulating RF circuits. For achieving optimum solutions, the product/PCB designer and the manufacturing engineer must appreciate the requirements of RF design.

Designing for High Frequencies

Designing a board to work at high frequencies requires the designer to be critical of the following areas:

- Material used for the PCB

- Placement of traces

- Placement of planes

- Component interconnections

RF PCBs can use a variety of different materials. Although common board materials used for high frequency circuits are FR-4 and derivatives of FR-4, many other base substrates are also used as they offer better electrical performance. These include specialized low-loss RF material such as pure PTFE, ceramic filled PTFE, Hydrocarbon Ceramic, and High-Temperature Thermoplastic/Ceramic.

Although FR-4 has its limitations when used for high-frequency work, the RF designer must understand these limitations and make cost/performance tradeoffs for the design. Typical limitations of FR-4 are:

- Stability of dielectric constant—Varying from lot to lot and over frequency

- Loss factor—Depending on surface contamination and the hygroscopic nature of the material

- Ability to withstand processing temperatures—Lead-free processing temperatures are higher than regular soldering temperatures

- Thermal conductivity—Even low-power RF circuits can produce a lot of heat

Fabrication Issues with Special Materials

All laminates mentioned above involve individual fabrication issues. For achieving the proper quality and reliability, the manufacturer must follow these individual fabrication notes for each substrate material for storing, handling, preparing the inner layer, surface preparation for photoresist application, bonding, drilling, deburring, and plating.

Manufacturers require setting up special processes for fabricating PCBs with low-loss RF materials to work at high frequencies. For instance, plated-through hole preparation is very critical for PTFE substrates—it needs an etch-back process requiring Plasma etch setup to prepare the PTFE hole surface and make it capable of accepting electroless copper plating. Therefore, apart from proper selection of material, following the proper fabrication methods is equally important for achieving a good quality PCB working reliably at high frequencies.

Placement of Traces

For matching the impedance, designers effectively manage the spacing of traces, ground planes, and the dielectric material to form a controlled impedance transmission line. They do this in several ways—in the form of a microstrip, stripline, co-planar waveguides, and differential pairs. The width of the trace, the dielectric thickness, dielectric constant of the used dielectric material and copper thickness determine the impedance. As high frequency signals are very sensitive to noise, ringing, and reflections, they must be designed with great care towards impedance. Mostly preferred impedance is 50 ohms for single ended and 100 ohms for differential, with control limits of ±10%.

Fig.1: Microstrip

Fig.2: Centered Stripline

Fig.3: Off-Center

Microstrip: This is a circuit trace carrying the RF signals routed on an outside layer of the PCB with a reference plane below it. The reference plane may be power or ground plane.

Stripline: This is a circuit trace carrying the RF signals routed on an inside layer of the PCB with two low-voltage reference planes above and below it. The reference planes may be power and or ground plane. The stripline can be equidistant from the two reference planes, in which case it is called the centered stripline, or it can be an off-center stripline, where it is closer to one of the reference planes.

Fig.4: Coplanar

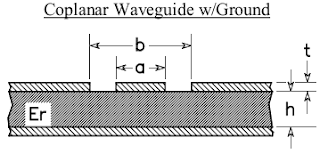

Fig.5: Coplanar Waveguide with Ground

Co-planar Waveguide: This is a circuit trace carrying the RF signals embedded within a ground reference plane on the same layer of the PCB. Co-planar waveguides (CPW) offer lower loss tangent than microstrips do, but have a higher skin effect loss, as fields concentrate on the edges of the trace and ground. Another form of co-planar waveguide is the co-planar waveguide with ground (CPWG), where a ground plane is placed just below the waveguide layer.

Fig.6: Coplanar Differential Pair

Fig.7: Coplanar Differential Pair with

Co-planar Differential Pairs: These are two traces carrying the RF signals embedded within a ground reference plane on the same layer of the PCB. This arrangement is also called the CP Differential Pair or Edge-Coupled CPW. This gives an extra degree of signal-to-noise isolation over the standard CPW. An added ground plane just below the layer offers even better field containment over the coupled CPW, and is called the Edge Coupled CPWG.

Placement of Planes

Most RF products use multilayer PCBs. These comprise a number of laminates of the substrate material separately etched, drilled, and bonded. The chief advantage of this is to allow the use of more than two conductor layers, thereby reducing the required board space, but at increased cost.

Setting up the laminates is a major part of the design for a multilayer RF board. The stack defines the number of layers the board will ultimately possess. At this stage, it is important to define the layers carrying specific high-speed tracks, and the placement of the ground and power layers with respect to those layers. Enclosing tracks carrying high frequency signals within the ground and power layers serves to define two significant factors related to high speed multilayer design—minimizing cross-talk, and maintaining a check on the impedance on the board. However, the cost of the board increases proportional to the number of layers it has, and therefore, the number of layers is usually a compromise of the board’s functionality and its cost.

RF products typically use a four or six layer FR-4 multilayer construction. Drilled and plated through holes or vias link tracks on one layer to tracks on other layers or all layers. Complex structures use blind or buried vias, with blind vias connecting the outermost layers to one or more inner ones, while buried vias connect only the inner layers and do not appear on the outermost layers. The third type of via is the through via, going through all the layers of the board. To create the connections, it is necessary to drill and then plate-through all vias. Via structures have a major effect on the fabrication processes of the PCB and contribute to the cost of the finished board.

Component Interconnections

Parasitic elements of a PCB refer to its physical attributes that affect the performance of the circuit. For instance, at high frequencies, a long thin track will usually be inductive, while a large pad over a ground plane will behave like a capacitor. In addition, when modeling in real circuits for, say a series capacitor, the designer must also include the impedance of the connections between the ground plane and circuit components.

A plated through via hole also adds significant inductance. RF designers can use good circuit simulation packages that include models to allow their addition. For instance, the typical inductance of a 0.2 mm diameter, 1.6 mm long hole can be as much as 0.75 nH. Although this may seem to be small, it can exert significant influence at high frequencies.

Components mounted on the PCB also contribute with their non-ideal characteristics. The use of Surface Mount Device (SMD) components helps to reduce the effect largely because of their reduced lead lengths and small construction, but the effect is still prominent at higher frequencies.

Designers use different ground plane strategies for their RF PCB design, and there is no unique solution as the best strategy. While most designers advocate breaking up the ground plane over the analog, digital, radio, and audio parts of the circuit, providing an individual ground plane of low impedance for all parts of the circuit is usually a good point to start.

Designers need to consider the flow of currents carefully throughout the product to minimize interferences between the audio and radio circuits. This assumes even greater significance if the design uses Digital Signal Processing (DSP) and microprocessors.

RF PCB Layout Strategies and Techniques

- Separate all RF, low-level analog, and digital sections.

- Divide the RF section into circuit groups (amps, LO, VCO, etc.).

- Place all the high-frequency components early in the layout, as this helps to minimize the length of the RF routes (in RF PCBs, functional orientation is more important compared to DFM).

- Place the components carrying the highest frequency next to the connectors.

- Never place unrelated inputs and outputs next to each other. For instance, multi-stage windings should never be placed adjacent.

- When long input or output to RF amplifiers is unavoidable, choose to make the output longer.

- As the trace impedance is a critical factor when trying to control reflections, always match the impedance between the driver and the load, except where the trace is shorter than 1/20th of the wavelength.

- When using pull-up inductors or resistors at the outputs of open-collector devices, always place the pull-up component next to the output pin it is pulling up.

- In addition to decoupling the main power pins of the IC, decouple the pull-up also.

- Inductors usually have large magnetic fields around them-

- Never placed them close together, when in parallel (unless the intention is to couple their magnetic fields)

- Separate all inductors by 1x times the body height (minimum) OR

- Place inductors perpendicular to one another

- Confine “ALL” routes to the section or stage to which they are assigned –

- Digital traces in the digital section

- Low-level analog traces in the low-level analog section

- RF traces in the RF section

- Routing traces into adjoining sections is not recommended

- Route all short RF traces on the component side of the PCB, rout them to eliminate vias

- Place a ground layer below the RF traces.

- Minimize the vias in the RF path, as this reduces the breaks in the ground plane(s) and –

- Minimizes inductance

- Helps contain stray magnetic and electric fields.

- Long controls lines are acceptable, but take care to route them away from RF inputs.

- Keep RF lines away from one another by a minimum distance to avoid unintended coupling & crosstalk.

- Minimum spacing is a function of the acceptable level of coupling, and is good for crosstalk, directional couplers, crosstalk, differential lines coupled in even or odd modes.

Summary

Finally, the design of a PCB and its fabrication for high frequency use is a complex process requiring intimate communication between the designer and the fabricator, with each understanding the issues related to high-speed design.

Fore More Details:

Url : https://www.pcbpower.com

Email: pcb@pcbpower.com

Phone: +91 7600012414